#### THE HISTORY OF THE MAINFRAME

#### Does This Look Familiar?

#### TABULATING MACHINES

#### IBM BEGINS THE FORMATION OF THE COMPUTER BUSINESS

- 1911 The Computing-Tabulating-Recording Company Starts (CTR)

- 1914 Thomas Watson, Sr. becomes the General Manager of CTR

- 1924 CTR renamed to International Business Machines with Thomas Watson, Sr. as its

CEO

- 1952 the IBM 701 Computer is developed becoming the first IBM commercial and scientific computer

- Wave of computers continue to be developed 1400, 1620, 7000 series...

- Upgrades, new models, of these machines and others came into existence.

#### 7000 SERIES OF MACHINES (LOOK FAMILIAR – MOVIE "HIDDEN FIGURES")

## SPREAD (SYSTEMS PROGRAMMING ENGINEERING AND DEVELOPMENT) TASK GROUP

#### Members

- J.W. Haanstra, Chairman

- B.O. Evans, Vice-Chairman

- Gene Amdahl

- J.D. Aron

- F.P. Brooks, Jr.

- J.W. Fairclough

- W.P. Heising

- H. Hellerman

- W.H. Johnson

- M.J. Kelly

- D.V. Newton

- B.G. Oldfield

- S.A. Rosen

- J. Svigals

#### HIGH LEVEL OUTCOME OF SPREAD

- Family of central processing units, each of which could handle both scientific and business applications

- Standard peripheral-device interfaces

- Unified Technology across the SPREAD plan

- Control Program that could be used on all processors in the family

- A single high-level language was called for that had scientific, business and advanced applications ability

- Increase memory size with the final design to address 16 million characters

- A 8-bit character called the 'byte' was selected for the basic alphanumeric structure.

#### S/360 ANNOUNCED ON APRIL 7, 1964

(MOST PEOPLE CONSIDER THE BIRTH OF THE MAINFRAME)

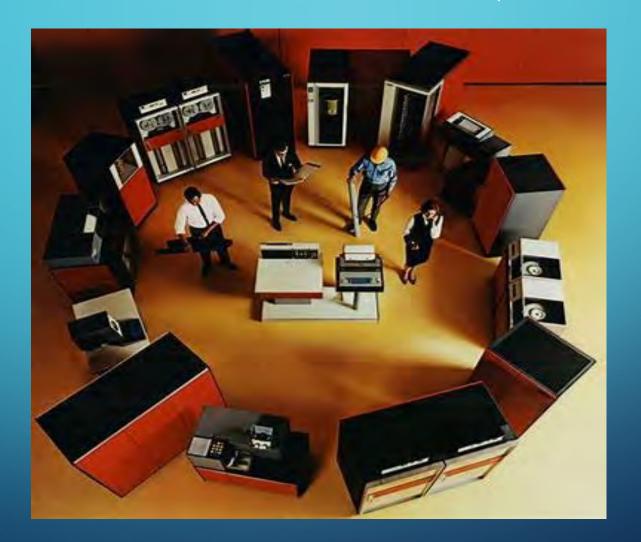

#### THREE ERAS OF MAINFRAMES

• The Solid State Logic Card Era (60's & 70's) (S/360; S/370; 303X)

• The Bipolar Era (80's & 90's) (308x; 3090; 9000)

• CMOS Era (Mid 90's to today) z1....z17......

The Solid State Logic Card Era (S/360; S/370; 303X)

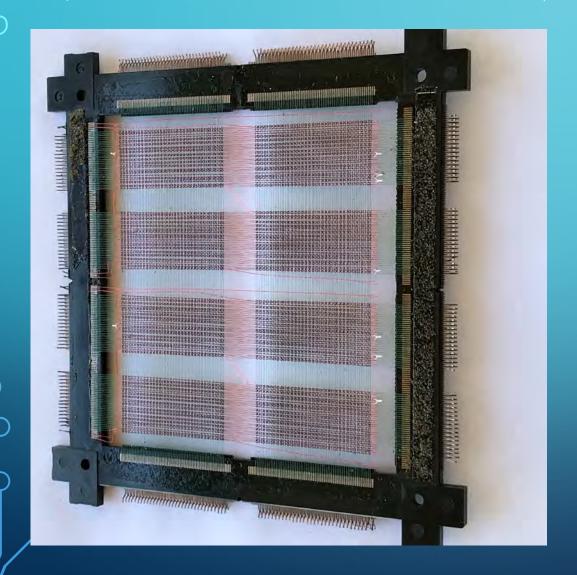

#### CORE MEMORY (16K BITS – STACK 9 OF THEM = 16K BYTES)

#### Components

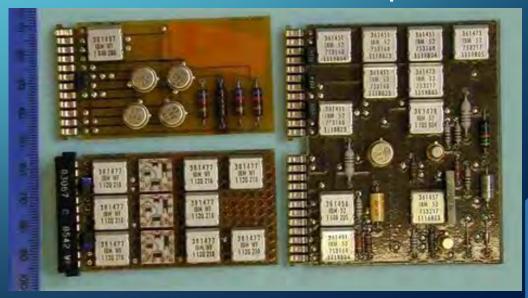

#### **Electronic Card Example**

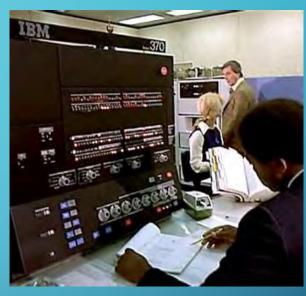

OPERATORS CONSOLE ON A S/360 & 370

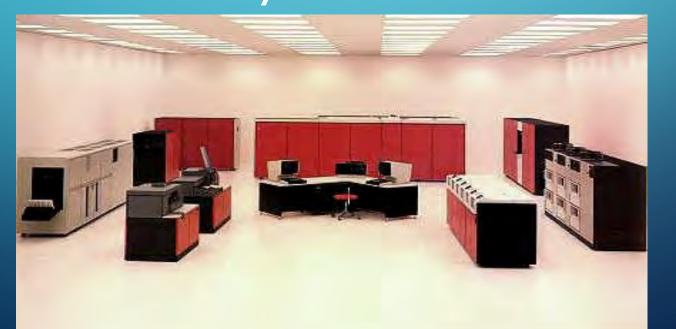

IBM System 3033

The Bipolar Era (80's & 90's)

(308x; 3090; 9000)

### MAINFRAMES A SUCCESS STORY FOR THE AGES

#### 3081 – 10 MIPS

#### THERMAL CONDUCTION MODULE (TCM)

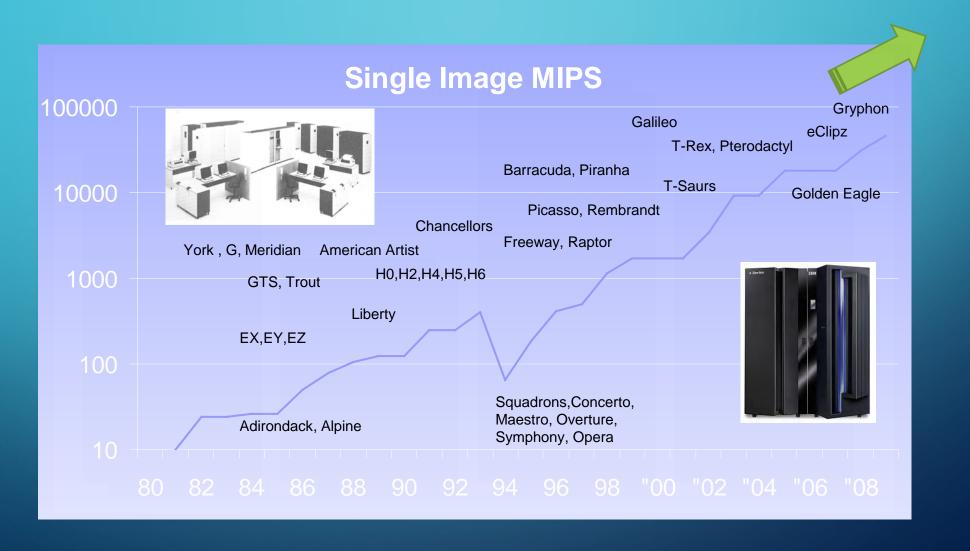

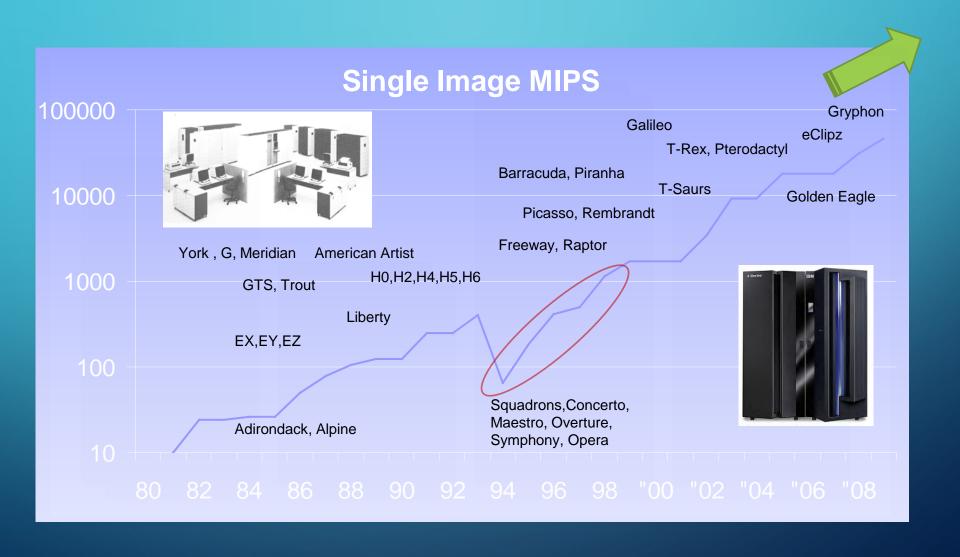

# CMOS Era (Mid 90's to today) z1....z17

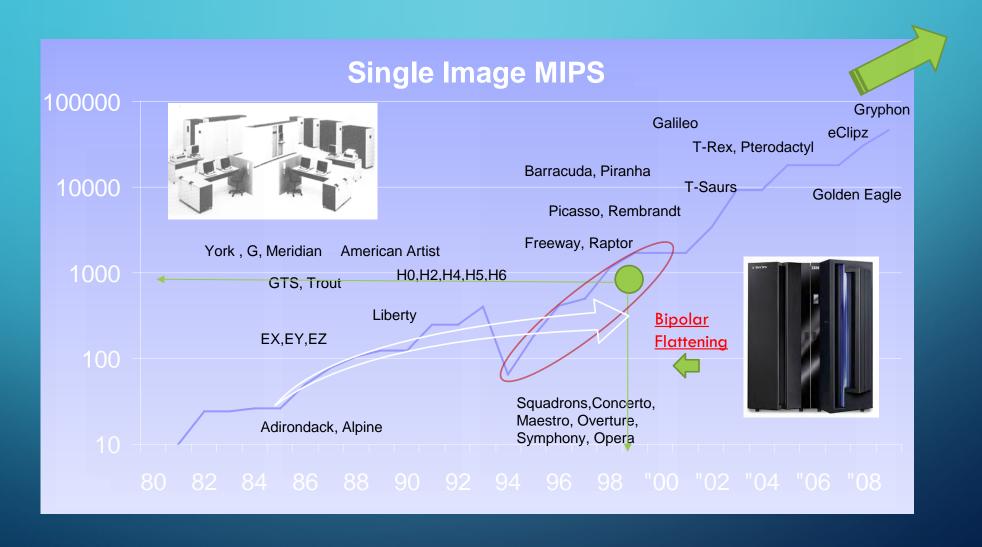

What Was Happening To The Mainframe Business In The Early 1990's

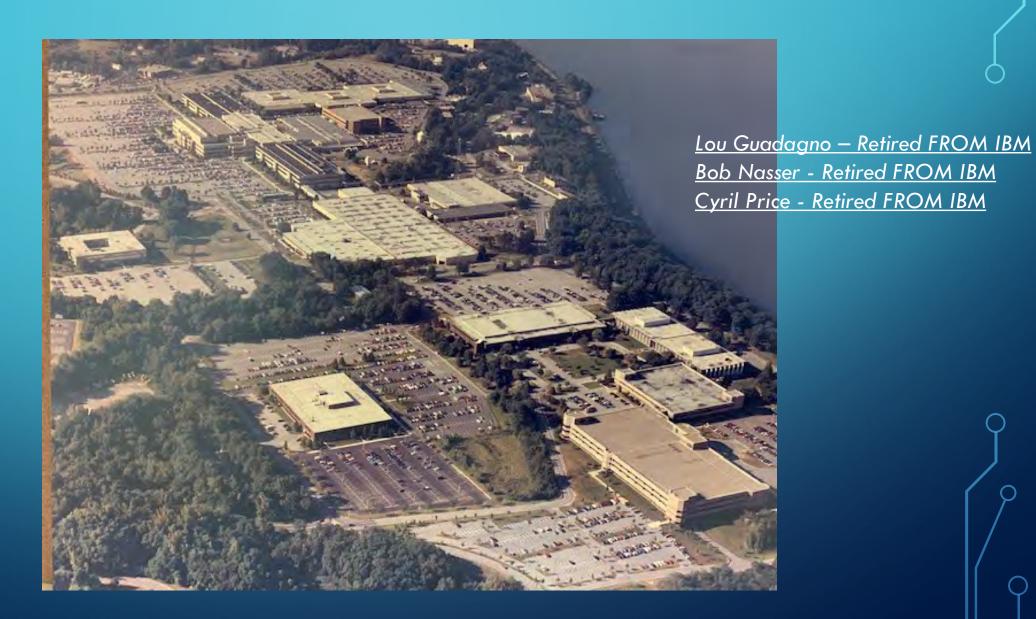

Lou Guadagno

- PC's were the "in thing"

- To build the next "turn of the crank" bipolar technology plant was unaffordable

- Bipolar was no longer following "Moore's Law" (2 times the performance every 18-24 mos)

- It was more like four years

- CMOS was, at the time, doing 2 times the performance every 18 months

- MAINFRAME IS DEAD "FRENZIE"

#### So What did we do?

- Major Change to the machine structure, switch to CMOS Technology and maintain and expand the architecture that was defined in the 1964.

- Resource Actions on ½ the workforce in the Hudson Valley

- Closed Kingston

- Shut down buildings all around the valley including East Fishkill

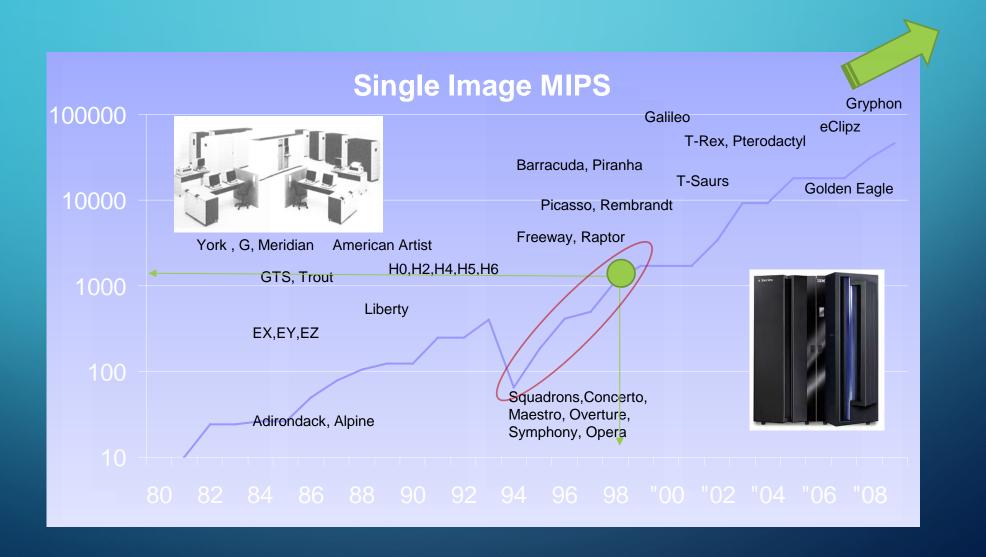

- Result was a major inflection in MIPS growth and the race was on of how we could get back on a par with where Bipolar was currently shipping with a lot fewer folks!

"SEA CHANGE"

## MAINFRAMES A SUCCESS STORY FOR THE AGES

**SEPTEMBER**

# Why Did We Need To Transition From Bipolar to CMOS Technology

Cyril Price

#### MULTIFACETED PROBLEM Required MULTIFACETED SOLUTION TRANSITION TO LOWER POWER CONSUMING CIRCUITS POWER DISSIPATION (WATER AND AIR COOLED) BIPOLAR TECHNOLOGY SIGNIFICANTLY CHALLENGED TO SUPPORT TRANSITION TO TECHNOLOGY WITH SIGNIFICANT GROWTH RAPIDLY INCREASING PERFORMANCE REQUIREMENTS POTENTIAL **PEOPLE - BUT NOT JUST TECHNOLOGY** REDUCE DEVELOPMENT REQUIREMENTS **UNAFFORDABLE DEVELOPMENT REQUIREMENTS OPTIMIZE DEVELOPMENT TEAM DROVE HIGH DEVELOPMENT EXPENSE SCHEDULE** SYSTEM DESIGN COMPLEXITY **IMPROVE SYSTEM DESIGN – ERROR CORRECTION REDUCED INSTRUCTION PROCESSING CYCLE TIME INSTRUCTION PROCESSING CYCLE TIME DESIGN SIMULATION PROCESS EFFICIENT DESIGN SIMULATION PROCESS TESTING** DEVELOPMENT ENGNEERING TEST **TIGHTER DEVELOPMENT / TEST / MFG INTEGRATION** MANUFACTURING TEST **PROGRAM MANAGEMENT IMPROVED PROGRAM MANAGEMENT**

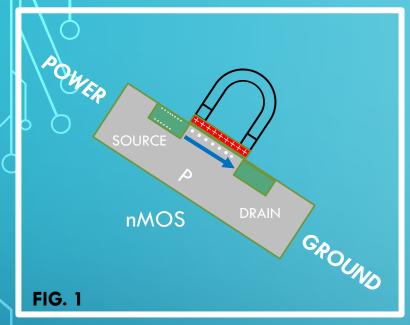

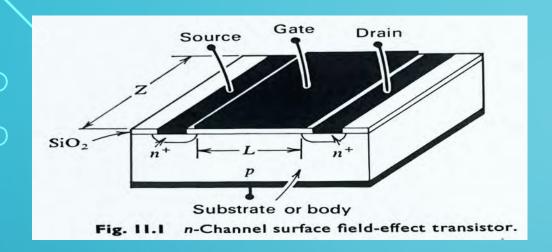

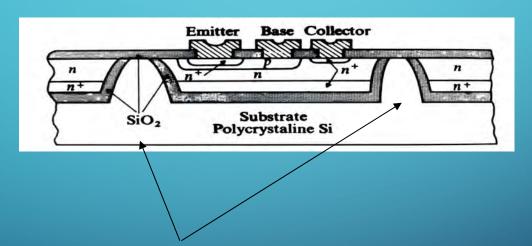

#### BIPOLAR TECHNOLOGY SEVERELY CHALLENGED

KEY DRIVER TO IMPROVEMENT - SEMICONDUCTOR TECHNOLOGY CHANGE

- BIPOLAR CIRCUITS USE NPN AND PNP TRANSISTORS

- HIGH TRANSIENT SWITCHING CURRENTS

- DCS Differential current switch

- ECL Emitter-coupled logic

- TTL Transistor-transistor Logic

- POWER DISSIPATION INCREASED TO INTOLERABLE LEVELS

- SINGLE IMAGE MIPS DROVE NEED FOR INCREASED CIRCUIT COUNTS

- RESULTS IN HIGHER HEAT GENERATION

- THERMAL CONDUCTION MODULES (TCM) USED TO COOL CHIPS

- ~ 2700 WATTS PER TCM

- BIPOLAR DEVICES ARE NOT PERFECT NPN / PNP JUNCTIONS

- LEAKAGE CURRENTS INCREASES WITH DECREASING DEVICE SIZE

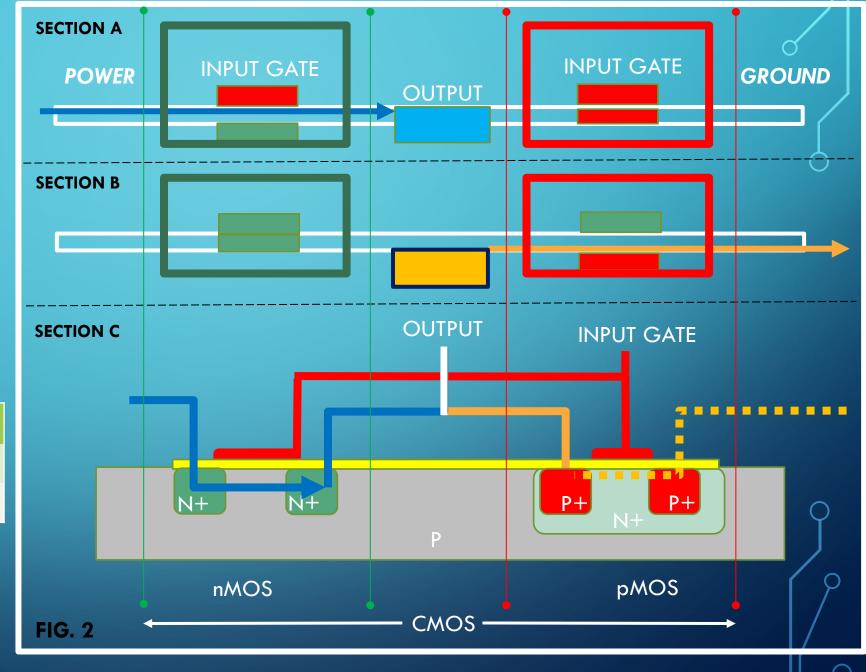

#### **CMOS**

| SECTION | INPUT<br>GATE | OUTPUT | INPUT<br>GATE | OUTPUT |

|---------|---------------|--------|---------------|--------|

| Α       | RED           | BLUE   | 0             | 1      |

| В       | GREEN         | ORANGE | 1             | 0      |

Very low static power dissipation Essentially only one device is on

CMOS is easier to fabricate. – Fewer layers

Denser than Bipolar – CMOS doesn't require isolation around devices

A single logic gate on a BIPOLAR chip can be comprised of a large number of components, as some extra components such as resistors are needed, while a single logic gate on a CMOS chip can be comprised of just two FETs.

#### SOLUTION - CMOS TECHNOLOGY

| TRANSITION TIMEFRAME H6/G4/G5 | BIPOLAR<br>TCM | CMOS<br>MCM     |

|-------------------------------|----------------|-----------------|

| CHIP COUNT                    | 5960           | 30              |

| MODULE COUNT/10 WAY           | 56             | 1               |

| MODULE SIZE                   | 110.5 X 117.5  | 127.5 x 127.5   |

| BOARD                         | 14             | 1               |

| CYCLE TIME                    | ??             | 3.5ns -> 2.5 ns |

| MIPS                          | ~ 465          | ~ 440 -> 1040   |

| MACHINE INTRODUCTIONS         | > 2 YEARS      | ~ 1 YEARS       |

| OPERATING TEMPERATURE RANGE   | 25 TO 70 °C    | -55 to 125°C    |

| NOMINAL SUPPLY VOLTAGE        | ~ 5V           | ~ 3 to 15 V     |

| FLOOR SPACE FT <sup>2</sup>   | 671.6          | 51.9            |

| MACHINE POWER (KVA)           | 144            | 5               |

| WEIGHT                        | 3185 <b>7</b>  | 2067            |

# MAINFRAME (Z SYSTEMS) TRANSITION IN THE 1990'S

LOU GUADAGNO – RETIRED FROM IBM

CYRIL PRICE - RETIRED FROM IBM

BOB NASSER - RETIRED FROM IBM

**SEPTEMBER**

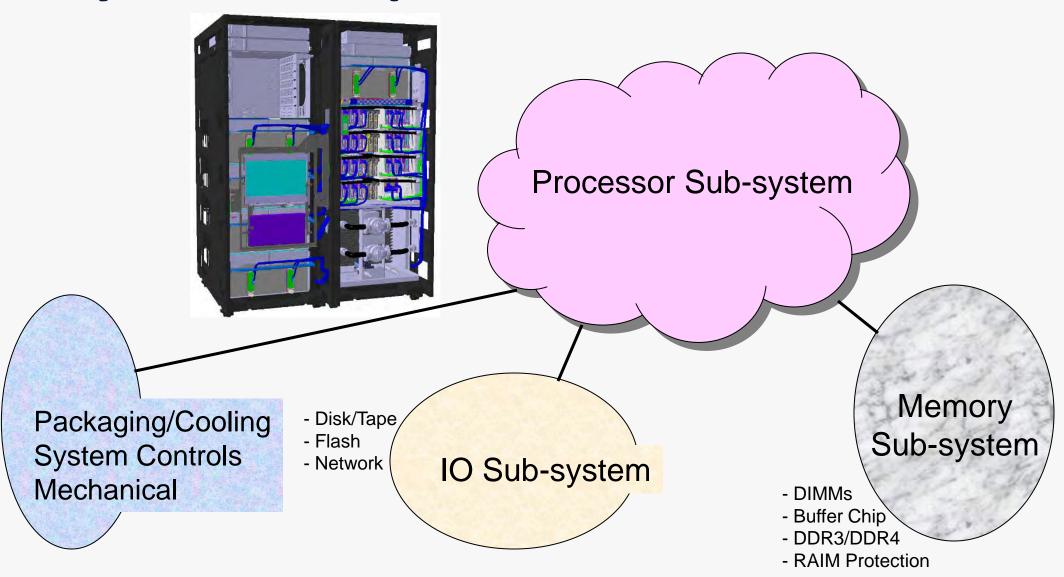

#### What Really Makes up A Mainframe

Lou Guadagno

#### z System Components

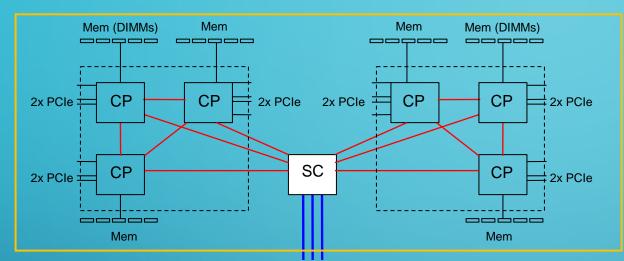

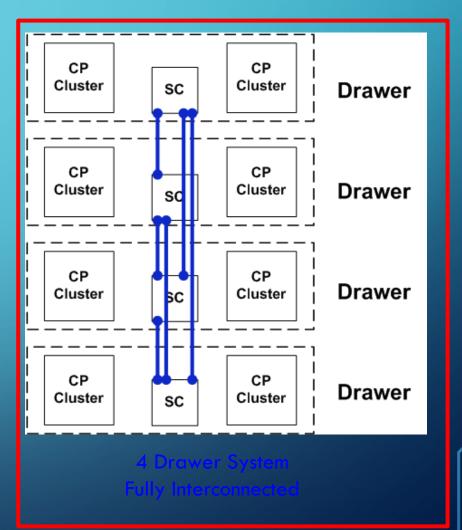

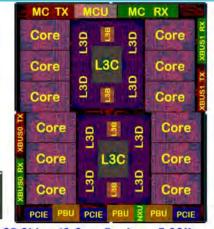

#### TOPOLOGY ON-DRAWER AND SYSTEM TOPOLOGY

To other drawers

CP chip, 696 sqmm, 14nm, 17 layers of metal

- 10 cores, each 2+4MB I+D L2 cache

- Shared 128MB L3 cache

SC chip, 696 sqmm, 14nm, 17 layers of metal

- System interconnect & coherency logic

- Shared 672MB L4 cache

#### Max System:

- 24 CP sockets in SMP interconnect

- 32TB RAIM-protected memory

- 40 PCI gen3x16 fanouts to IO-drawers

- 320 IO cards

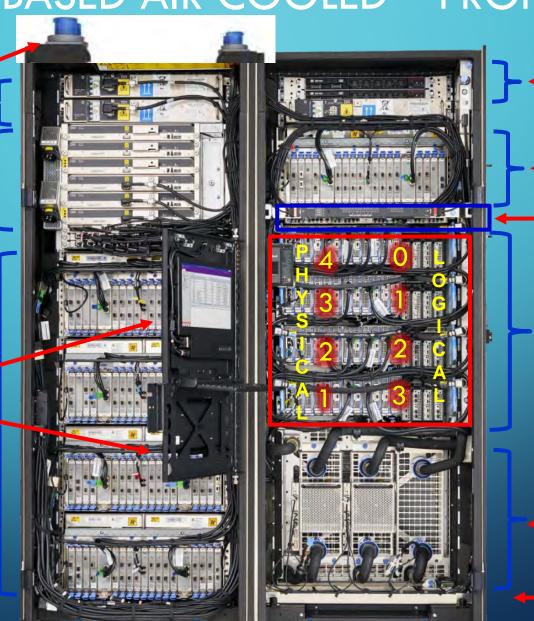

#### 214 RADIATOR-BASED AIR COOLED - FRONT VIEW

Overhead Power Cables (option)

> Internal Batteries (optional)

> > Power Supplies

Displays and keyboards for Support Elements

PCle I/O drawers numbers 1 to 4

2 x 1U Support Elements

PCle I/O drawer number 5

System Control Hubs (used to be BPHs)

CPC Drawers, PCle Fanouts, Cooling water manifold and pipes, PCle I/O interconnect cables, FSPs and Ethernet cables

Note: CPC Drawer plugging numbers are on the left and logical numbers on the right

Radiator Pumps

Overhead I/O feature is a co-req for overhead power option

LOU GUADAGNO – RETIRED FROM IBM CYRIL PRICE - RETIRED FROM IBM BOB NASSER - RETIRED FROM IBM

**SEPTEMBER**

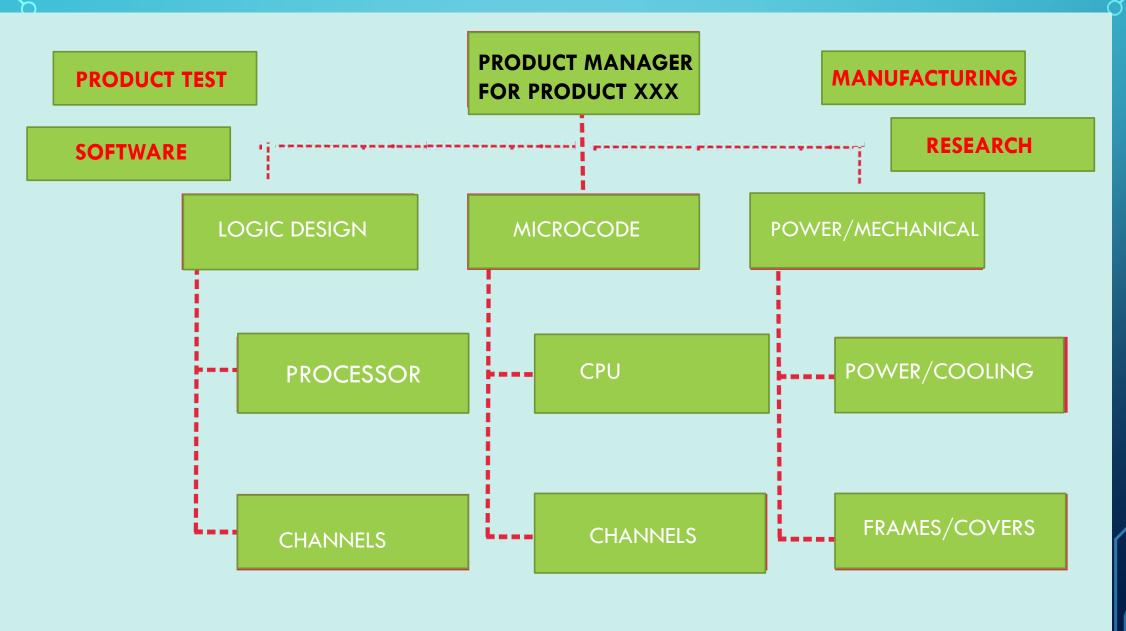

Change Of Methodology Of Managing Machine Development/Manufacturing To The "Program Management" Model **Bob Nasser**

#### THE WAY WE WERE - CIRCA 1969

Product Development was owned by a single organization

#### TRADITIONAL STRUCTURE

## PRODUCT DEVELOPMENT IN MULTIPLE LOCATIONS

- POUGHKEEPSIE High End Mainframes

- KINGSTON Printers, Displays, Telecommunication Products

- ENDICOTT Midrange Mainframes

- BOEBLINGEN, GERMANY Low End Mainframes, Memory

### **ADVANTAGES**

- CENTRALIZED CONTROL EVERYONE UNDER THE SAME MANAGAMENT

- GEOGRAPHICALLY LOCATED EVERYONE IN THE SAME LOCATION

- SUPPORT ORGANIZATIONS LOCATED LOCALLY

- PRODUCT TEST

- MANUFACTURING

- PROCUREMENT

- •

### **DISADVANTAGES**

REDUNDANT SKILLS ACROSS MULTIPLE LOCATIONS

- DUPLICATION OF SUPPORT PROCESSES

- "NIH" ATTITUDE "NOT INVENTED HERE"

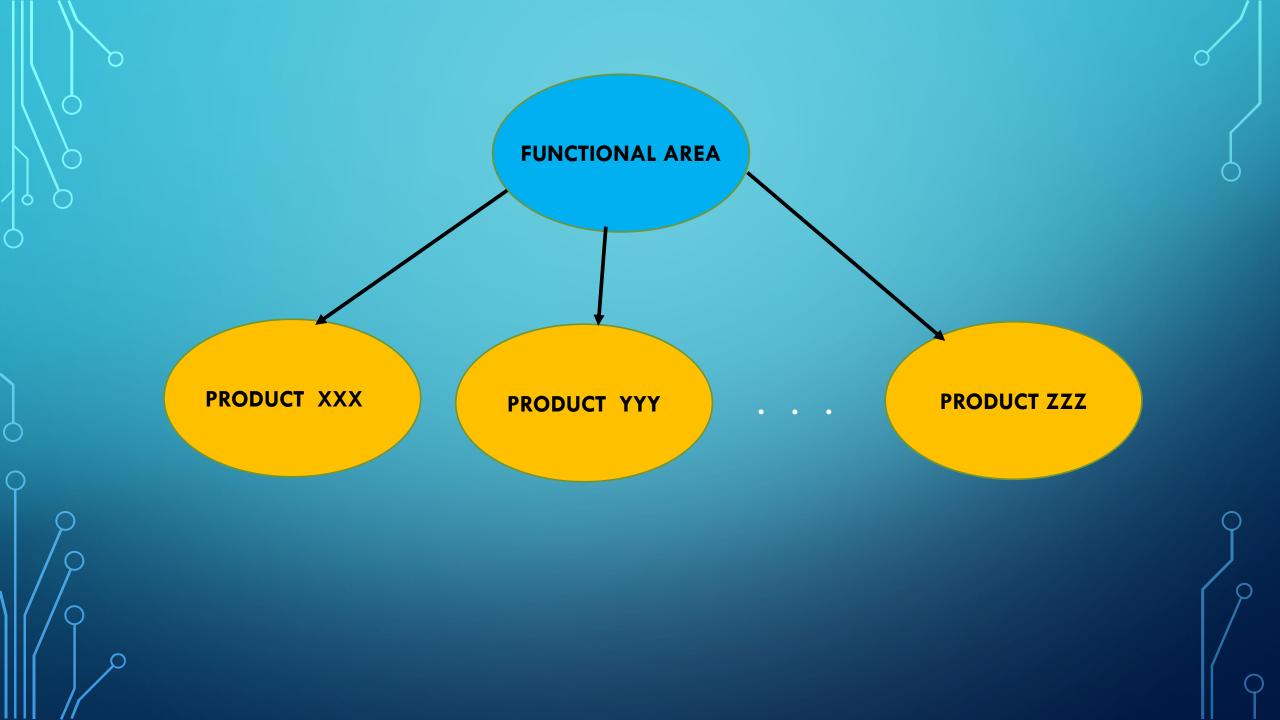

EVOLUTION TO THE WAY WE ARE NOW

1993 - NEW CEO, LOU GERSTNER, DECLARES:

"IBM WILL BECOME A PROJECT BASED ORGANIZATION"

A NEW CAREER PATH CREATED: PROJECT MANAGER

PREVIOUSLY SKILL ORIENTED:

ENGINEER, PROGRAMMER, TECHNICIAN, . . .

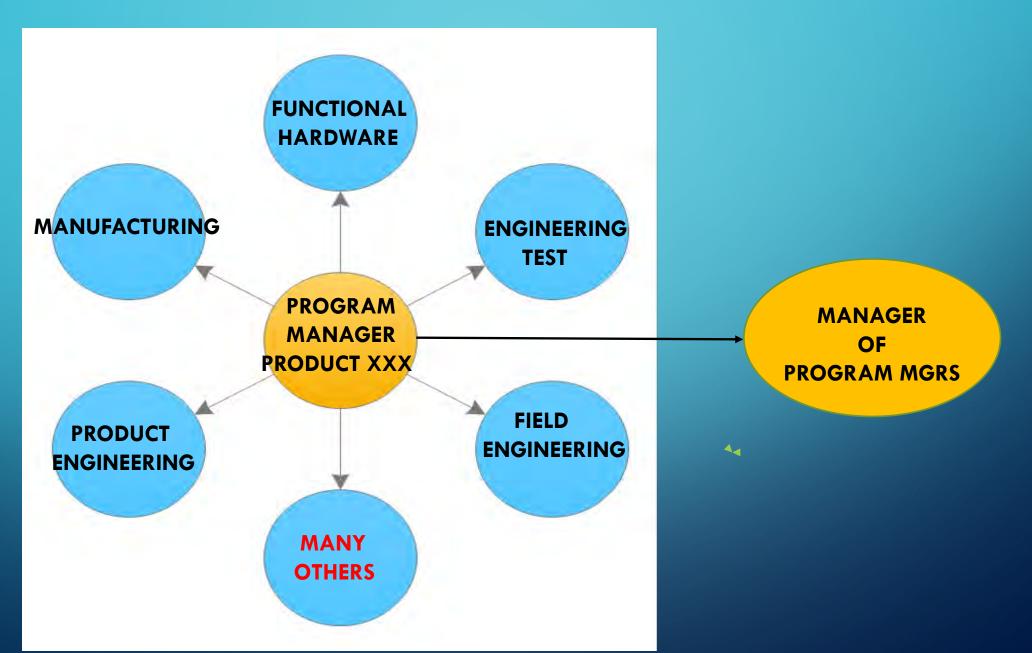

### **MATRIX - WHEEL AND SPOKE**

### **ADVANTAGES**

- CENTERS OF COMPETENCY FOR CRITICAL SKILLS

- SOURCE FOR SKILLS FOR EACH PRODUCT.

- COMMON METHODOLOGIES AND SUPPORT PROCESSES

- ELIMINATED "NIH" ATTITUDE.

### **DISADVANTAGES**

- GEOGRAPHIC AND TIME ZONE DIFFERENCES.

- WORK DAY EXPANSION

- POUGHKEEPSIE AND GERMANY 6 HOURS APART

- POUGHKEEPSIE, GERMANY, JAPAN 12 HOUR DIFFERENCE

- MORE FREQUENT TRAVEL

- PERIODIC IN-PERSON MEETINGS TO PROMOTE TEAM BUILDING

**SEPTEMBER**

Division Of Workload and Workforce Interaction Methodology Changes To Accomplish What Seemed Like An Impossible Challenge

## MAINFRAMES A SUCCESS STORY FOR THE AGES

## WHAT WAS THE ENVIRONMENT LIKE

- We had just lost ½ the workforce.

- We were staffed in five sites (Poughkeepsie/Boeblingen/Endicott/Yorktown Research).

- There was some feeling of stress of who would take the lead in Developing this new wave of computers => Poughkeepsie or Boeblingen.

- Great deal of pressure to recover the Bipolar MIPS, keep our Customers committed to us as we went through the transition, and maintain this wonderful business for IBM to be the legendary franchise it was and will be in the future.

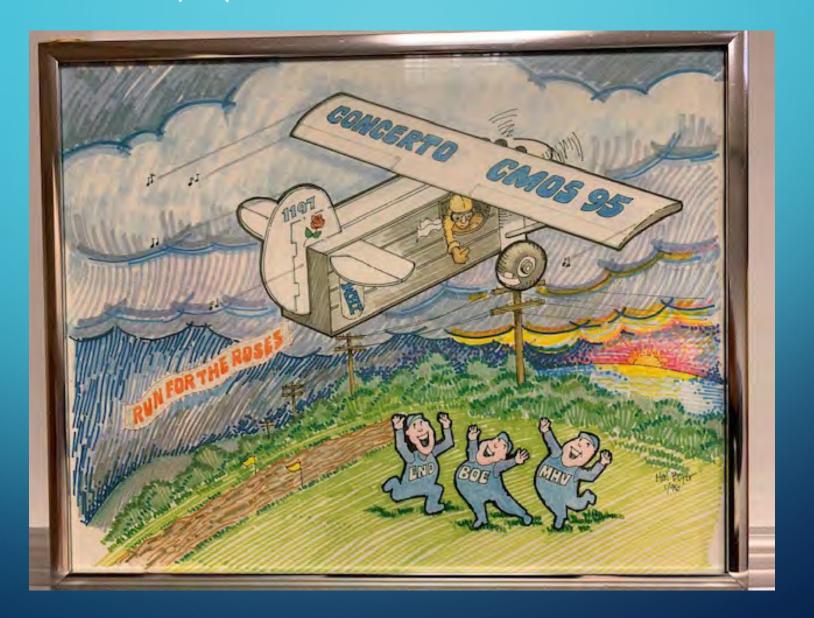

### WHAT BECAME OUR HIGH LEVEL PLAN

- Develop and ship 4 machines in 4 consecutives years

- Concerto 1995

- Maestro 1996

- Overture 1997

**Bipolar Threshold**

- Symphony 1998 =>1000 MIPS

- This would far exceed the biggest Bipolar we ever shipped

- Send a message to our Customers and the World that we could be counted on to be relevant to the times and their needs now and in the future.

## HOW WERE WE GOING TO DO THIS WITH THE WORK FORCE WE HAD

- Define two microprocessor teams

- One in Boeblingen who already had developed the initial stages of a microprocessor to be used on Concerto and Maestro

- Second team here in Poughkeepsie/Kingston had started to develop a new microprocessor for Overture and Symphony

- Divide the remainder of the work between Poughkeepsie, Boeblingen and Endicott (I/O, Power/Thermal/Mechanical, Memory, microcode etc.) for all machines

- Use the "Program Management" Model to execute the plan Worldwide.

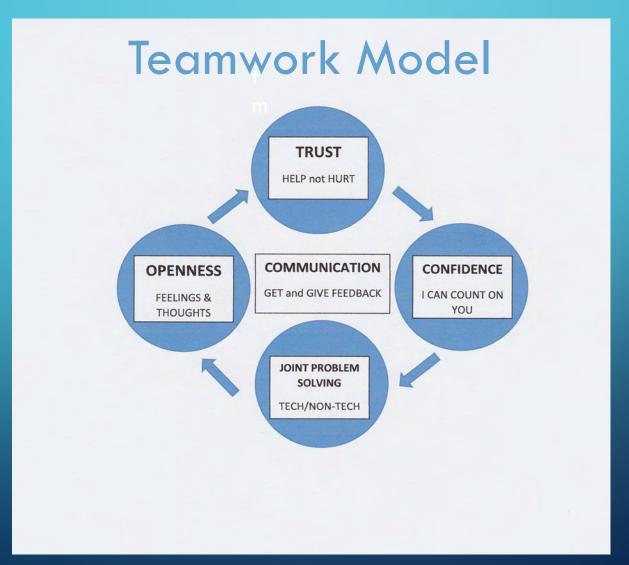

## IT WAS GOING TO TAKE MORE THAN JUST A PLAN FOR THE WORK!

- Needed a level of unparalleled teamwork

- Leadership from all three sites including Montpellier from both

Development and Manufacturing met in Triberg, Germany

- In the middle of the Black Forest

- This is where Cuckoo clocks are made

- Bonded and developed a teamwork model to pull it off.

## THEME TO OPERATE AS A WORLDWIDE TEAM AFTER 1993 MAJOR RESOURCE ACTION.

## IN 1995 CONCERTO – G2 (Z2 IN TODAYS TERMINOLOGY) 186 MIPS

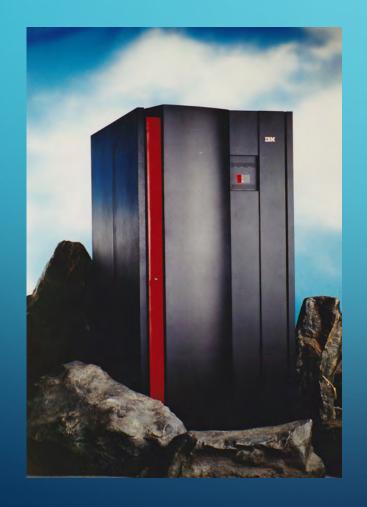

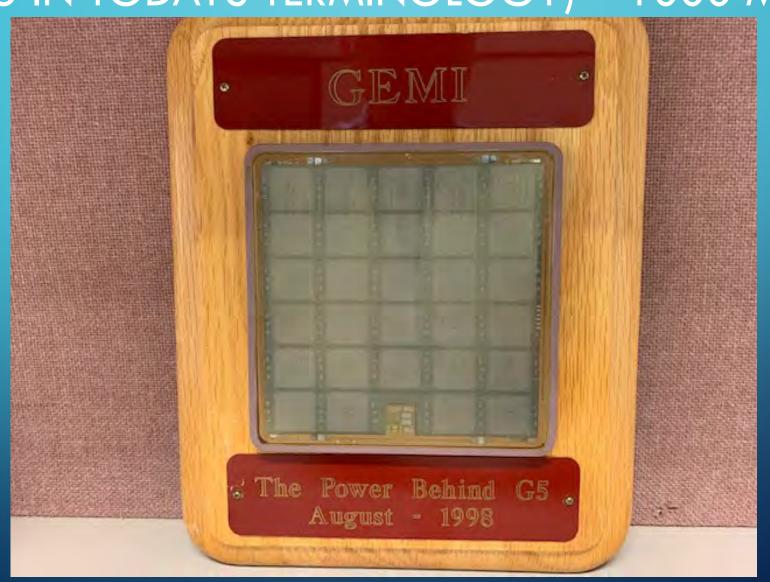

# IN 1998 SYMPHONY – G5 (Z5 IN TODAYS TERMINOLOGY) 1000+ MIPS

S390 G5 and G6

#### WORLD'S LEADING BUSINESSES RUN ON THE MAINFRAME (CIRCA 2019)

92

of the top 100 worldwide banks

10

out of 10 of the world's largest insurers

23

of the top 25 US retailers

23

out of 25 of the world's largest airlines

**Mainframes process**

30 billion business transactions per day

Mainframes enable

\$6 trillion in card payments annually

**80 percent** of the world's corporate data resides or originates on mainframes

**91 percent** of CIOs said new customer-facing apps are accessing the mainframe

Rick Schoonmaker

IBM Z and LinuxONE HW Product Management Director roschoon@us.ibm.com

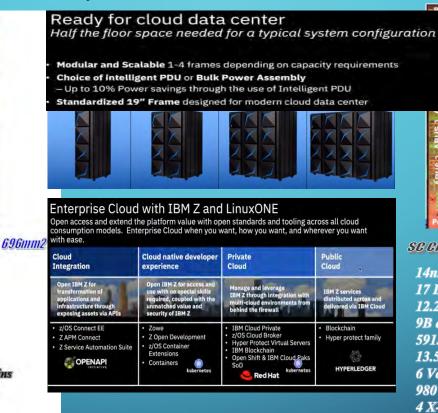

## MAINFRAME IS CRUCIAL IN THE WORLD TODAY

70%

of all transactions by value go through an IBM mainframe<sup>1</sup>

\$8.5T

Value of U.S. payments being processed on mainframe<sup>2</sup>

99.99999%

industry-leading availability equivalent to 315ms of downtime per year <sup>3</sup>

## FULLY ENGINEERED STACK FOR AI WHERE IT MATTERS MOST

Transaction processing platform

Operating systems & firmware

IBM Z infrastructure

Built on a foundation of security, resiliency, and high availability.

450 billion

Inference operations per day with 1 ms response time vs. 300B on IBM z168

7.5x Al throughput

Utilizing 8 Al processing units vs. one on IBM z169

250K MIP's

## SYMPHONEY - G5 (Z5 IN TODAYS TERMINOLOGY) — 1000 MIPS

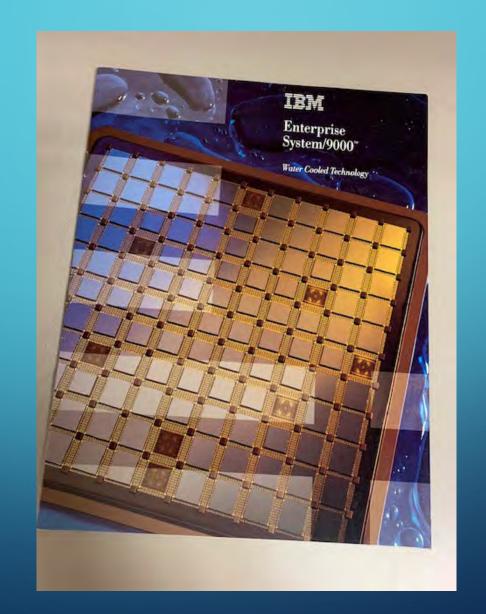

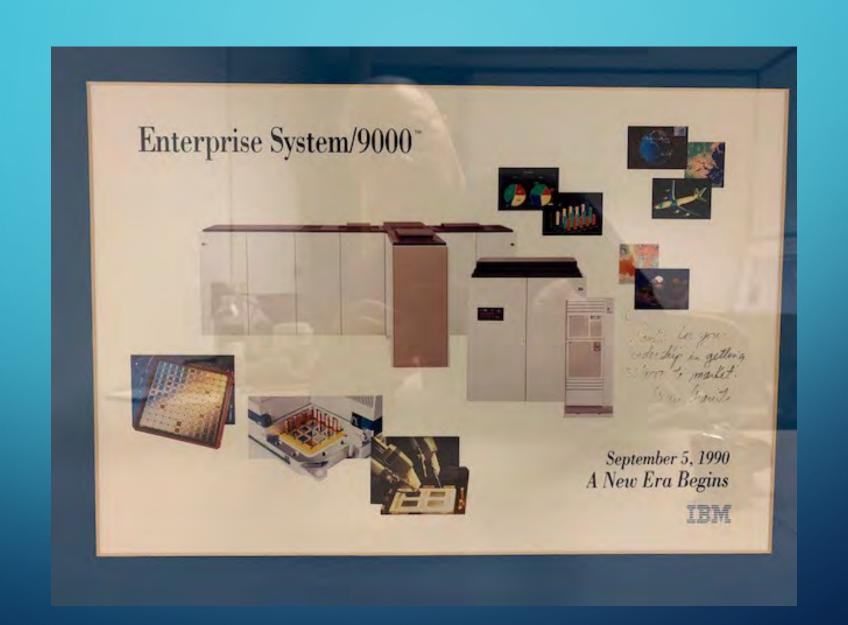

## MODULE FOR 9000 SERIES MAINFRAMES

#### Special Edition

Full-color, pull-out poster included in center pages.

November 1980

New IBM system announced today

#### IBM 3081 takes a major evolutionary step into the future

The IBM 308' processor announced The JBM 305 i protrises assumed holy represent a major revolutionary for a few computer age and a giant ship life the fitters as insensed by the advanced technologies. It brings to sure in the marketplace.

For JBM, and expectably for the desired by the second by the

tireless efforts of countless indo stuals.

"The credit for this new processor,"

says Jack Bertram, IBM vace president and DSD president, "belongs to everyone - not only those in DSD directly involved in the immediate task, but also those who provided support services of every kind both within end without the division.

"I doubt if there has ever been a ew ISM product amountement hose access depended so much on e interaction of so many employees so many different sites,"

This endeavor's recknological roots he traced back nearly a decade, a result of the revolutionary techby it incorporates, the IBM 3081 es lower post, higher performance The 3081 processor uses 60 percent time.

nuder these companisons. blast face comparison.

Timediate Consertations.

greater reliability than any other iem energy and discipates 55 percent And largely because of its compact- disrupting their data processing workless heat - significant cost and emi-ness, IBM customer engagers will be load. ronmental considerations.

able to install it in 24 hours compared Equally important, the IBM 3081

tantial improvement in overall house for IBM customers who are 370 family, it uses the same software thermal conduction module (TCM). reformance with improved smill-constantly adding new applications — control programs (MVS and VM) to it can turn out far more work in less customers can migrate easily from

aternal operating apped of the The processor occupies 55 percent less Yet, for all these improvements, the reliability. This is largely the result of 233. And, of course, a offers floor space even though - as a work- IBM 3081 is still part of the System/ an ingenious package, known as the

Continued on page 36,

#### e this issue:

- tage from IBM Chairman

- . The marketing viewpoint: page 4.

- mail conduction module: The IBM 3033 Model Group S announced: page 5.

- erio article on the IBM East Fishkill articles begin on: The quality assurance effort: page 8.

- A missage from DSD President

Poughkeepsie articles begin on:

Field engineering: page 32.

- . Planning: page 29.

- Data Systems Assurance: page 30.

- · MRL and corporate componer procurement: page 33.

- . Endicott's new board: pages 34-3

- Design practices: page 36.

## MAINFRAMES A SUCCESS STORY FOR THE AGES

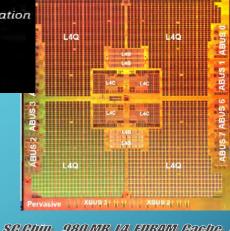

#### z15 Processor and Storage Controller Chips, Modules, Systems

#### 215 CP Chip. 12-Core Design. 5.2GHz

14nm SOI Technology, Chip Power: 282 W

17 BEOL Wiring Layers 12 Cores With Dedicated L1 & L2 Cache

8MB Private L2 Cache

9.2 Billion Devices

4.0 Billion eDRAM Cells

189 Million SRAM Cells

15.6 Miles of Wire 26.2B Vias 6 Pwr Domains

7 Clock Domains Shared 256MB L3 Cache

5 Port Memory Interface

2 X-Bus Interfaces

3 PCI Express Interfaces GEN-4

SC Chip 980 MB 14 EDRAM Cache 696mm2

14nm SOI Technology, Chip Power: 100W 17 BEOL Wiring Layers

12.2 Billion Devices

9B eDRAM Cells

591.8 million signal nets 18M SRAM Cells

13.5 Miles of Wire, 22.3B Vias

6 Voltage Domains, 5 Clock Domains,

980 MB L4 Cache

4 X-Bus Interfaces

IBM Z team delivered a system that is 40% smaller than previous z14s, but with increased 4 A-Bus Interfaces capacity and 14% single thread performance improvement! This coupled with increases of up to 190 cores in a single system, ultimately delivers a 25% max system capacity increase, which means our clients can now execute a huge 1 trillion web transactions per day!

Z SYSTEMS (A.K.A. MAINFRAME - DEF.): AN INTEGRATED, HIGHLY SCALABLE COMPUTER SYSTEM THAT ALLOWS MANY DIFFERENT PIECES OF WORK TO BE HANDLED AT THE SAME TIME, SHARING THE SAME INFORMATION AS NEEDED WITH PROTECTION, HANDLING VERY LARGE AMOUNTS OF INFORMATION FOR MANY USERS WITH SECURITY, WITHOUT USERS EXPERIENCING ANY FAILURES IN SERVICE.

### THE 165 MIPS G3 (Z3) REQUIRED UNPRECEDENTED TEAMWORK